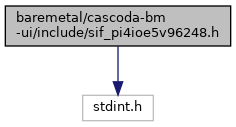

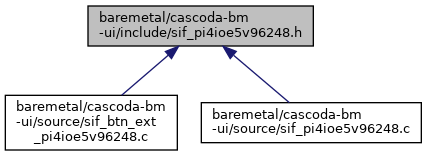

#include <stdint.h>

Go to the source code of this file.

◆ I2C_PORTNUM

◆ SIF_PI4IOE5V96248_ALL_PINS_MASK

| #define SIF_PI4IOE5V96248_ALL_PINS_MASK 0xFF |

◆ SIF_PI4IOE5V96248_I2C_ADDR

| #define SIF_PI4IOE5V96248_I2C_ADDR 0x20 |

◆ SIF_PI4IOE5V96248_INT_PIN

| #define SIF_PI4IOE5V96248_INT_PIN 5 |

◆ SIF_PI4IOE5V96248_NO_PIN_MASK

| #define SIF_PI4IOE5V96248_NO_PIN_MASK 0x00 |

◆ SIF_PI4IOE5V96248_PIN_0_MASK

| #define SIF_PI4IOE5V96248_PIN_0_MASK 0x01 |

◆ SIF_PI4IOE5V96248_PIN_1_MASK

| #define SIF_PI4IOE5V96248_PIN_1_MASK 0x02 |

◆ SIF_PI4IOE5V96248_PIN_2_MASK

| #define SIF_PI4IOE5V96248_PIN_2_MASK 0x04 |

◆ SIF_PI4IOE5V96248_PIN_3_MASK

| #define SIF_PI4IOE5V96248_PIN_3_MASK 0x08 |

◆ SIF_PI4IOE5V96248_PIN_4_MASK

| #define SIF_PI4IOE5V96248_PIN_4_MASK 0x10 |

◆ SIF_PI4IOE5V96248_PIN_5_MASK

| #define SIF_PI4IOE5V96248_PIN_5_MASK 0x20 |

◆ SIF_PI4IOE5V96248_PIN_6_MASK

| #define SIF_PI4IOE5V96248_PIN_6_MASK 0x40 |

◆ SIF_PI4IOE5V96248_PIN_7_MASK

| #define SIF_PI4IOE5V96248_PIN_7_MASK 0x80 |

◆ SIF_PI4IOE5V96248_PORT_0

| #define SIF_PI4IOE5V96248_PORT_0 0x00 |

◆ SIF_PI4IOE5V96248_PORT_1

| #define SIF_PI4IOE5V96248_PORT_1 0x01 |

◆ SIF_PI4IOE5V96248_PORT_2

| #define SIF_PI4IOE5V96248_PORT_2 0x02 |

◆ SIF_PI4IOE5V96248_PORT_3

| #define SIF_PI4IOE5V96248_PORT_3 0x03 |

◆ SIF_PI4IOE5V96248_PORT_4

| #define SIF_PI4IOE5V96248_PORT_4 0x04 |

◆ SIF_PI4IOE5V96248_PORT_5

| #define SIF_PI4IOE5V96248_PORT_5 0x05 |

◆ SIF_PI4IOE5V96248_RST_PIN

| #define SIF_PI4IOE5V96248_RST_PIN 6 |

◆ SIF_PI4IOE5V96248_T_RESET

| #define SIF_PI4IOE5V96248_T_RESET 1 /* 1 ms for reset */ |

◆ expand13_alarm_state

| Enumerator |

|---|

| SIF_PI4IOE5V96248_INT_TRIGGERED | |

| SIF_PI4IOE5V96248_INT_CLEARED | |

◆ expand13_status

| Enumerator |

|---|

| SIF_PI4IOE5V96248_ST_OK | |

| SIF_PI4IOE5V96248_ST_FAIL | |

◆ SIF_PI4IOE5V96248_Acquire()

| uint8_t SIF_PI4IOE5V96248_Acquire |

( |

uint8_t * |

port0 | ) |

|

◆ SIF_PI4IOE5V96248_alarm_triggered()

| uint8_t SIF_PI4IOE5V96248_alarm_triggered |

( |

void |

| ) |

|

◆ SIF_PI4IOE5V96248_Initialise()

| uint8_t SIF_PI4IOE5V96248_Initialise |

( |

void |

| ) |

|

◆ SIF_PI4IOE5V96248_Sense()

| uint8_t SIF_PI4IOE5V96248_Sense |

( |

uint8_t |

io, |

|

|

uint8_t * |

val |

|

) |

| |

◆ SIF_PI4IOE5V96248_SetOutput()

| uint8_t SIF_PI4IOE5V96248_SetOutput |

( |

uint8_t |

io, |

|

|

uint8_t |

val |

|

) |

| |