Loading...

Searching...

No Matches

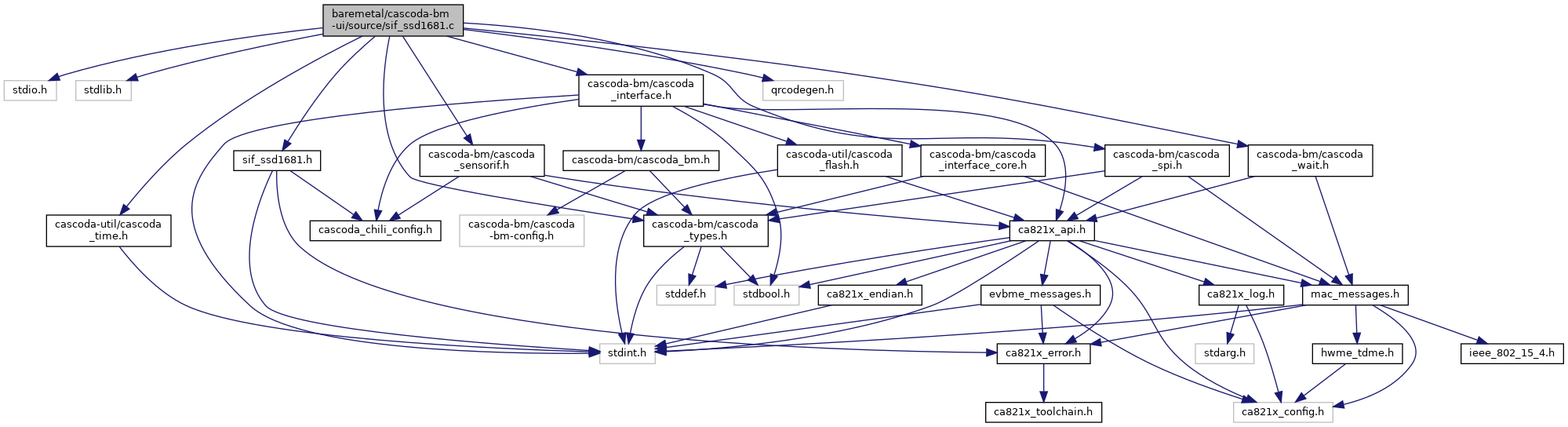

#include <stdio.h>#include <stdlib.h>#include "cascoda-bm/cascoda_interface.h"#include "cascoda-bm/cascoda_sensorif.h"#include "cascoda-bm/cascoda_spi.h"#include "cascoda-bm/cascoda_types.h"#include "cascoda-bm/cascoda_wait.h"#include "cascoda-util/cascoda_time.h"#include "qrcodegen.h"#include "sif_ssd1681.h"

Include dependency graph for sif_ssd1681.c:

Functions | |

| bool | SIF_SSD1681_IsAsleep (void) |

| Function which reports the sleep status of the eink display. | |

| ca_error | SIF_SSD1681_Initialise (void) |

| EINK Initialisation. | |

| void | SIF_SSD1681_Deinitialise (void) |

| EINK De-Initialisation. | |

| void | SIF_SSD1681_ClearDisplay () |

| Clears the display. | |

| void | SIF_SSD1681_StrongClearDisplay (void) |

| Clears the display many times to make sure there is no ghost image. | |

| void | SIF_SSD1681_DeepSleep (void) |

| Enter deep sleep mode. | |

| ca_error | SIF_SSD1681_overlay_qr_code (const char *text, uint8_t *image, uint8_t scale, uint8_t x, uint8_t y) |

| Creates a QR code and overlays it on top of a pre-existing image at the given coordinates. | |

| void | SIF_SSD1681_SetFrameMemory (const uint8_t *image, bool full_resolution) |

| Copies the image into the eink display's RAM, for full update. | |

| void | SIF_SSD1681_SetFrameMemoryPartial (const uint8_t *image) |

| Copies the image into the eink display's RAM, for partial update. | |

| void | SIF_SSD1681_DisplayFrame (void) |

| Causes the eink to display what is currently in its RAM, using the full update process. | |

| void | SIF_SSD1681_DisplayPartFrame (void) |

| Causes the eink to display what is currently in its RAM, using the partial update process. | |

| void | SIF_SSD1681_DisplayPartBaseImageWhite (void) |

| Causes the eink to display a white image, to be used as a "base" image for subsequent partial updates. | |

Macro Definition Documentation

◆ BOOSTER_SOFT_START_CONTROL

| #define BOOSTER_SOFT_START_CONTROL 0x0C |

◆ BORDER_WAVEFORM_CONTROL

| #define BORDER_WAVEFORM_CONTROL 0x3C |

◆ DATA_ENTRY_MODE_SETTING

| #define DATA_ENTRY_MODE_SETTING 0x11 |

◆ DEEP_SLEEP_MODE

| #define DEEP_SLEEP_MODE 0x10 |

◆ DISPLAY_UPDATE_CONTROL_1

| #define DISPLAY_UPDATE_CONTROL_1 0x21 |

◆ DISPLAY_UPDATE_CONTROL_2

| #define DISPLAY_UPDATE_CONTROL_2 0x22 |

◆ DRIVER_OUTPUT_CONTROL

| #define DRIVER_OUTPUT_CONTROL 0x01 |

◆ MASTER_ACTIVATION

| #define MASTER_ACTIVATION 0x20 |

◆ SET_DUMMY_LINE_PERIOD

| #define SET_DUMMY_LINE_PERIOD 0x3A |

◆ SET_GATE_LINE_WIDTH

| #define SET_GATE_LINE_WIDTH 0x3B |

◆ SET_RAM_X_ADDRESS_COUNTER

| #define SET_RAM_X_ADDRESS_COUNTER 0x4E |

◆ SET_RAM_X_ADDRESS_START_END_POSITION

| #define SET_RAM_X_ADDRESS_START_END_POSITION 0x44 |

◆ SET_RAM_Y_ADDRESS_COUNTER

| #define SET_RAM_Y_ADDRESS_COUNTER 0X4F |

◆ SET_RAM_Y_ADDRESS_START_END_POSITION

| #define SET_RAM_Y_ADDRESS_START_END_POSITION 0X45 |

◆ SIF_SSD1681_BOTTOM_EDGE_HEIGHT

| #define SIF_SSD1681_BOTTOM_EDGE_HEIGHT (SIF_SSD1681_HEIGHT_PHYSICAL - SIF_SSD1681_WIDTH_WINDOW) |

◆ SIF_SSD1681_BOTTOM_EDGE_WIDTH

| #define SIF_SSD1681_BOTTOM_EDGE_WIDTH (SIF_SSD1681_WIDTH_PHYSICAL) |

◆ SIF_SSD1681_RIGHT_EDGE_HEIGHT

| #define SIF_SSD1681_RIGHT_EDGE_HEIGHT (SIF_SSD1681_HEIGHT_PHYSICAL) |

◆ SIF_SSD1681_RIGHT_EDGE_WIDTH

| #define SIF_SSD1681_RIGHT_EDGE_WIDTH (SIF_SSD1681_WIDTH_PHYSICAL - SIF_SSD1681_WIDTH_WINDOW) |

◆ SW_RESET

| #define SW_RESET 0x12 |

◆ TEMPERATURE_SENSOR_CONTROL

| #define TEMPERATURE_SENSOR_CONTROL 0x1A |

◆ TERMINATE_FRAME_READ_WRITE

| #define TERMINATE_FRAME_READ_WRITE 0xFF |

◆ WRITE_LUT_REGISTER

| #define WRITE_LUT_REGISTER 0x32 |

◆ WRITE_RAM

| #define WRITE_RAM 0x24 |

◆ WRITE_RAM_RED

| #define WRITE_RAM_RED 0x26 |

◆ WRITE_VCOM_REGISTER

| #define WRITE_VCOM_REGISTER 0x2C |